반응형

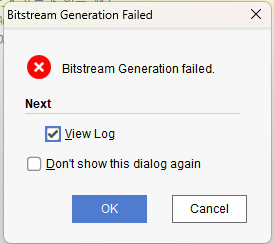

Bitstream Generation failled ?? 일때?

Synthesis(합성)는 성공했는데 Bitstream Generation만 실패했다면

대부분 Implementation(구현) 단계에서 문제가 발생한 것!!

Synthesis(합성)는 단순히 논리 설계가 맞는지 확인하는 단계고

Bitstream 은 실제 칩에 회로를 배치(Placement)하고 배선(Routing)하는 과정!!

# 자주 발생하는 원인 및 해결방법

| 원인 | 해결 방법 |

| I/O Pin 미지정 | 모든 입력/출력 핀이 .xdc 파일(Constraints)에 정의되어 있는지 확인 = 하나라도 빠지면 비트스트림이 생성되지 않음. |

| Voltage 설정 누락 | CFGBVS나 CONFIG_VOLTAGE 설정이 없다는 에러가 뜬다면, .xdc 파일에 관련 set_property 문구를 추가 |

| Timing 실패 | 설계한 회로가 너무 복잡해서 설정한 클럭 속도를 맞추지 못할 때 발생 = 로직을 단순화하거나 클럭을 낮춰 |

반응형

'전기전자 찌릿 > FPGA' 카테고리의 다른 글

| [ FPGA ] Basys 3 Artix 7 FPGA - Seven Segment를 이용한 카운터 -2 (0) | 2026.02.12 |

|---|---|

| [ FPGA ] Basys 3 Artix 7 FPGA - Seven Segment를 이용한 카운터 -1 (0) | 2025.10.18 |

| [ FPGA ] Basys 3 Artix 7 FPGA - 논리 Gate 이용한 LED on off -4 (0) | 2025.10.10 |

| [ FPGA ] Basys 3 Artix 7 FPGA - 논리 Gate 이용한 LED on off -3 (0) | 2025.10.09 |

| [ FPGA ] Basys 3 Artix 7 FPGA - 논리 Gate 이용한 LED on off -2 (0) | 2025.10.08 |